1. LEON プロセッサについて

最

初の LEONは、 ESA (European Space Agency : 欧州宇宙機関)

で開発され、1999年に発表されています。宇宙で使用される半導体はアルファ粒子放射線や宇宙線放射線の影響でメモリやレジスタの値が変更されてしまう

SEU(Single Event Upset)現象が起きてしまう可能性があります。 LEON

は宇宙船でも使用できるように、このSEUの対策を行ったプロセッサとして開発されました。アーキテクチャとしてオープンなSPARCを採用しています。

GNU general public Licenseで公開されました。

そ

の後、チーフデザイナーであった、jiri Gaislerは、ESAを離れ、gaisler

research社を設立し、LEONの開発を続けています。LEON2はSEU部分を取り除いたものが

LGPLライセンスでソースコード公開されました。その際には、プロセッサの周辺IPも接続された形で公開されています。LEON3はコマーシャルライセ

ンスとGPLライセンスの2種類のライセンスがあります。多数の周辺IPと一緒にgaisler researchのHP( www.gaisler.com)からダウンロードすることができます。一部の高機能IPはコマーシャルライセンスのみとなっていますが、大多数の周辺IPもGPLライセンスで使用することができます。

LEON3の特徴として以下のようなことが挙げられます。

1. FPGAのみならず、ASICとして動作実績がある(Silicon proven)。

SPARC internationalより、公式にSPARC V8 Architecture準拠の承認を取っています。

SPARC向けのバイナリがあるソフトウェアなら問題なく動作します。

ソフトウェア、ハードウェアともオープンソースでありながら、信頼性が高いです。

2. 多数の周辺IPコアが同一環境でオープンソースライセンスで公開されています。

(Ethernet MAC, GPIO, memory contoller, AHB/APB bridge, AMBA controller, PCI, UART, JTAG, PS/2, CAN, I2C,....)

これらのコアが接続されたSoCとしてソースコードが公開されています。

約50種類ある、公式サポートFPGAボードを使えば、そのまま簡単にシステムを動作させることができます。

またIPの接続の変更もGUIで簡単に行えます。

3. ライセンスはオープンなGPLを用いています(いわゆるオープンソースハードウェア)。

プロセッサ初め、Ethernetコア等のIP郡のRTLを読むことができるため非常に勉強になります。

Xilinx, Altera, actel, ASICどれでも簡単にマッピングできるようになっている。

コマーシャルライセンスも準備されています。

(他のソース公開できないIPと一緒に使用して商品を開発する場合はライセンスを購入することになります。)

以上のように非常に魅力のあるオープンソースハードウェアです。

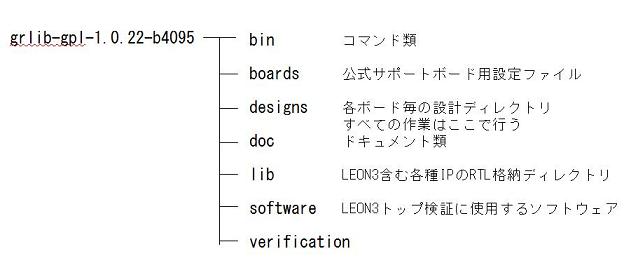

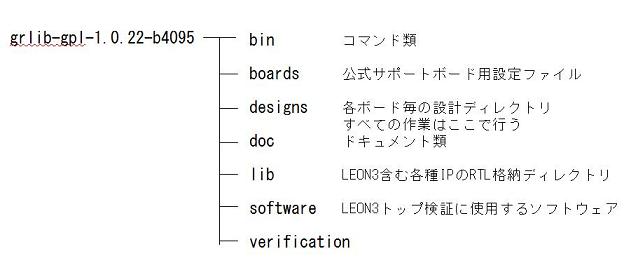

2. ソースコードのダウンロードとディレクトリ構造

まず最初にソースコードをダウンロードしてきます。

gaisler research の HPのdownloadコーナーより、GRLIBをダウンロードします。LEON3 もGRLIBの中の一つとして含まれています。

今現在のダウンロードファイル名は、 grlib-gpl-1.0.22-b4095.zip です。

(しばしばバージョンアップされています。)

また、GRLIB user's manualもダウンロードします。基本的にこのドキュメントに従えばFPGAにLEON3システムをマッピングすることができます。

GRLIBの基本的なプラットフォームOSは Linux です。私はVMware server上に CentOS 5 をインストールしてそこで使用しています(VMware serverもCentOS5も無料です)。

(cygwin

やmsysを用いたwindows上での実行も可能ですが、cygwinのmakeコマンドにバグがあるようで、Linux版と比較すると不安定です。私

は、開発する際にxilinx版のmodelsimを使用したかったためmsys環境も少し使用しましたが、一部ファイルを修正したりする必要がありまし

た(xilinx modelsim無料版はwindowsのみ提供)。

とりあえず、FPGAにマッピングしてLinuxをブートさせるまで行うのはLinux上でできますので、Linuxでの操作になれてからWindows環境に移ることをお薦めします。)

まず、最初にこれからLEON関連の開発環境を作っていくためのディレクトリを作成します。

mkdir LEON

cd LEON

ダウンロードしてきたファイルをこのディレクトリに移動して解凍します。

unzip grlib-gpl-1.0.22-b4095.zip

解凍した結果、以下のようなディレクトリ構成になります。

様々なディレクトリがありますが、実際に作業を行うのはdesigns以下のディレクトリのみです。そこからMakeコマンドで必要なものを自動的に集めるような仕組みが組み込まれています。

cd designs

にて designsディレクトリに移動すると、約50種類のFPGAボード毎のディレクトリが存在しています。

最

初にLEONシステムを使用する際には、ここにある約50種類のFPGAボードの内のどれか一つを使用することを強く勧めます。というのも、ここに挙げら

れているFPGAボードであれば、そのボードに合わせた周辺IPを接続したSoCがピン配置を含め完全に準備されているので、makeコマンドのみで

FPGAコンフィグファイルが生成できます。

最初にLinuxをブートさせるまでを簡単に体験すれば、全体像を理解するまでの時間が大幅に短縮できます。

有名なボードが多数サポートされています。

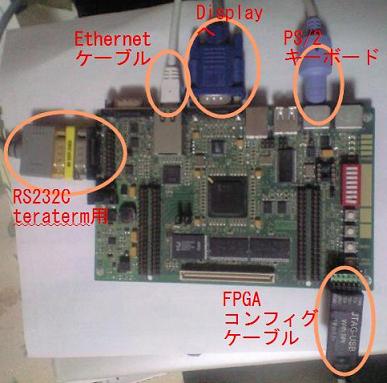

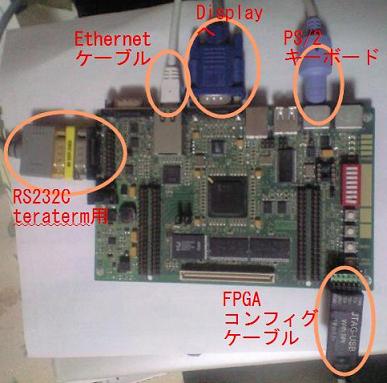

私

の持っているFPGAボードは GR-XC3S-1500 というものです。これは gaisler research の協力会社である

pender electronics という会社が発売しているものです。その他にも altera NEEKや xilinx

ML501等の一般的なボードも多数サポートされています。

以降のエントリでは、GR-XC3S-1500 における作業を記述していきます。

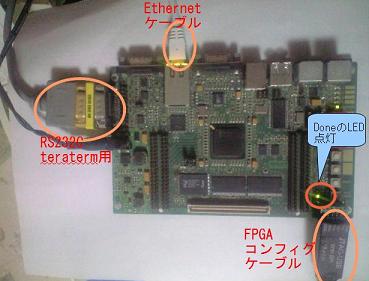

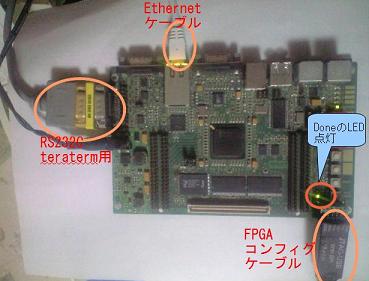

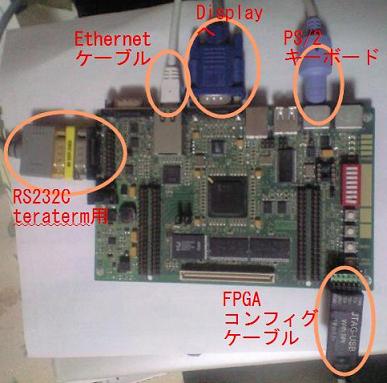

GR-XC3S-1500の写真を載せておきます。

私は標準添付のXilinx impact用のコンフィグケーブルを紛失してしまったため、digilent社のJTAG-USBケーブルを購入してFPGAのコンフィグケーブルとして使用しています。

3. 必要なソフトウェアとダウンロード

FPGAにLEONシステムをマッピングして、Linuxをブートさせるために必要なソフトウェアをインストールします。

GRLIBは様々なEDAツール等をサポートしていますが、ここでは最低限のものをインストールします。

このエントリはXilinx FPGAを用いた場合です。

使用するソフトウェアは以下のものです。

(1) Xilinx ISE WebPack (Linux版)

(2) GHDL simulator

(3) Bare-C cross compiler system for LEON

(4) GRMON Debug Monitor for LEON systems

(5) snapgear linux for LEON

(6) LEON GLibC Cross-compiler (gnu tool chain)

(1)は、Xilinx社提供のFPGAマッピングツールの無料版です。

XilinxのHPからダウンロードしてインストールします。Version11.4がgaisler researchより公式推奨されていますので、そちらをインストールします。

(2)は、有名なオープンソースVHDLシミュレータです。

GHDLのHPからダウンロードしてインストールします。GUIによってLEONシステムをコンフィグレーションした後にシステム動作確認プログラム込みで全体のRTLをシミュレーションしてシステムの整合性を確認するために使用します。

(3)

は、OS無しで動作するLEONプロセッサ用のCコンパイラです。GHDLでシミュレーションする動作確認プログラムをコンパイルするのに使います。ま

た、コンパイルした後のバイナリは、シミュレーションだけでなく実機でも動作しますので、FPGAコンフィグ後のハードウェアチェックにもつかえます。

gaisler researchのHPからダウンロードしてインストールします。

(4)

は、FPGA上にマッピングされたLEONシステムとホストコンピュータから通信するために使用するソフトウェアです。評価版がgaisler

researchから公開されています。このソフトウェアを通して、プログラムやLinuxのバイナリをFPGA上のメモリに転送します。また、FPGA

上のレジスタの値等を見ることができます。

gaisler researchのHPからダウンロードしてインストールします。

(5)は、LEONシステム用のLinuxソースコードです。kernelのバージョンは2.6です。

gaisler researchのHPからダウンロードしてインストールします。

(6)は、LEONシステム上のLinux用コンパイラです。Linuxをソースコードからコンパイルしてバイナリファイルを作成する時に使用します。

gaisler researchのHPからダウンロードしてインストールします。

以上のソフトウェアをインストールしたら準備完了です。

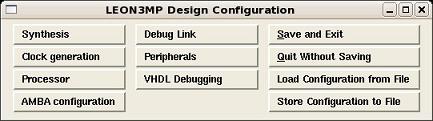

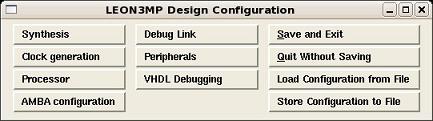

4. LEONシステムのコンフィグレーション

必要なソフトウェアのインストールが終わったら、LEONシステムのコンフィグレーションを行います。

cd designs/leon3-gr-xc3s-1500

でボード用の開発ディレクトリに移動します。

このディレクトリには、Makefileが準備されていて、必要な作業はMakeコマンドで行えるようになっています

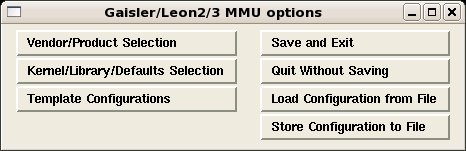

make xconfig

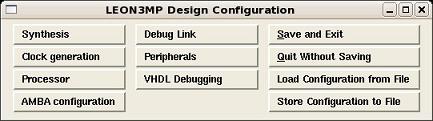

と打ち込むとGUIが立ち上がります。

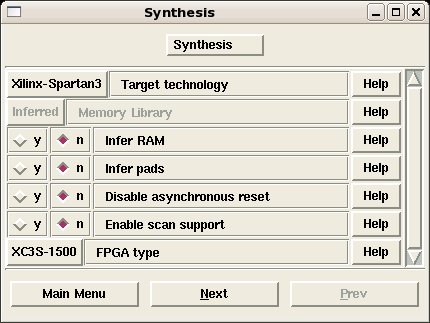

基本的に、このボードに合わせたコンフィグレーションがすでに行われているので変更しなくても良いのですが、Synthesisから順に見ていきます。

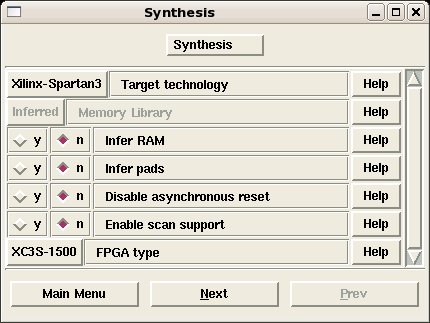

Synthesisと書かれたボタンをクリックすると以下のようなGUIウィンドウが立ち上がります。

このディレクトリでGUIを立ち上げた時点で、GR-XC3S-1500に合わせた設定が行われています。

Target technologyには、Xilinx-spartan3が選択されています。

ここでは、何も変更する必要はありません。

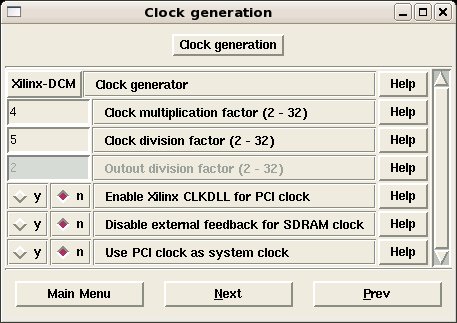

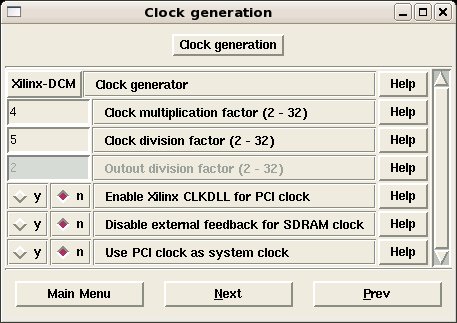

そこで Next のボタンをクリックすると、次の Clock generation 設定GUIが立ち上がります。

クロック生成に関する設定項目が出てきますが、ここでも何もいじる必要はありません。

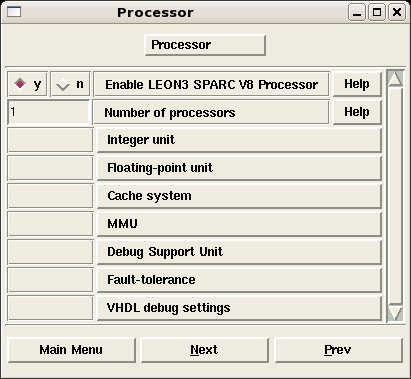

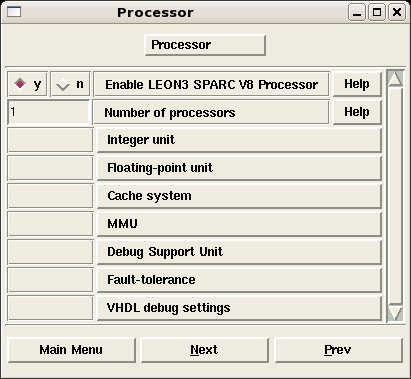

Next のボタンをクリックすると Processor のコンフィグレーション設定GUIが立ち上がります。

プロセッサに関してはコンフィグレーション可能項目が多数存在します。

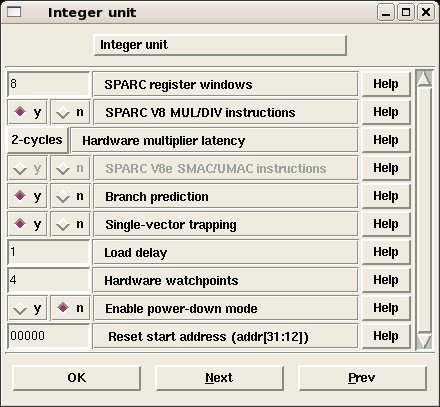

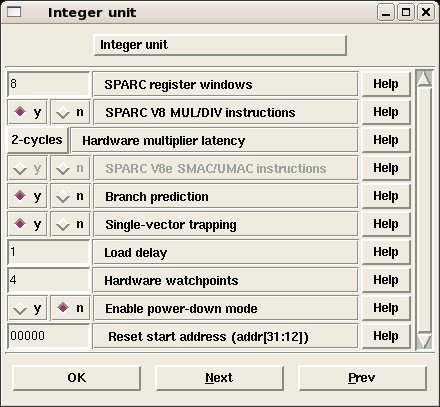

まず、 Next のボタンをクリックすると、Integer unitの設定GUIが立ち上がります。

ここでも基本的にこのまま設定を変更しません。

最初の設定項目は、SPARCアーキテクチャ特有のregister windowの数です。

次は SPARC V8 MUL/DIV命令を実装するかどうかの選択です。実装しなかった場合乗算除算は別の小さな命令の集合でコンパイラが実現します。ここの設定によってコンパイラへ与えるオプションが変わります。

その他、分岐予測を行うかどうか等を設定できます。

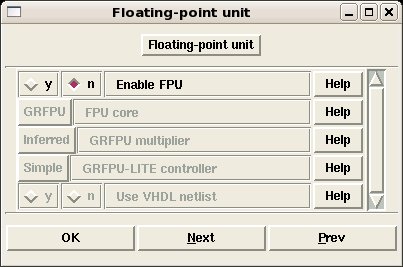

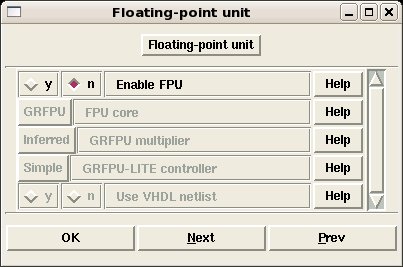

次に Next のボタンをクリックすると、FPU(Floating point unit)の設定GUIウィンドウが立ち上がります。

FPU

は、GPLライセンスでソースコード公開されておらず、コマーシャルライセンスが必要となります。ただし、Xilinx,

Alteraで使用する際には、マッピングされたネットリストを評価ライセンスとして公開されています。これをダウンロードしてくれば、FPGAにマッピ

ングして使用することは可能です。今回はFPUは使いません。

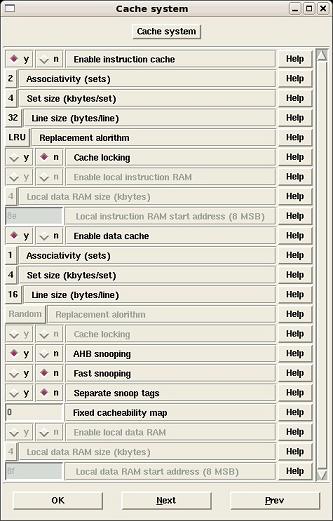

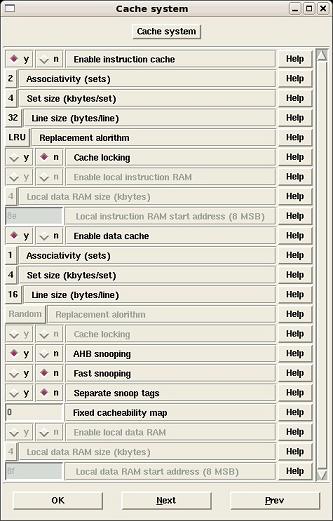

Nextボタンをクリックするとキャッシュの設定GUIウィンドウが立ち上がります。

instruction cache, data cacheそれぞれに細かいコンフィグレーションが可能です。キャッシュ無しにすることもできます。キャッシュのサイズ、way数等を設定できます。

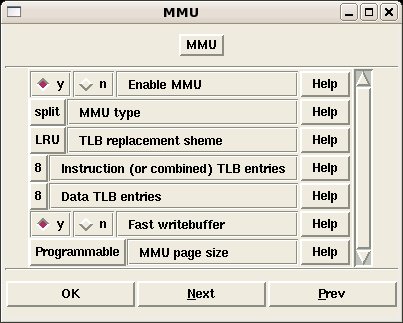

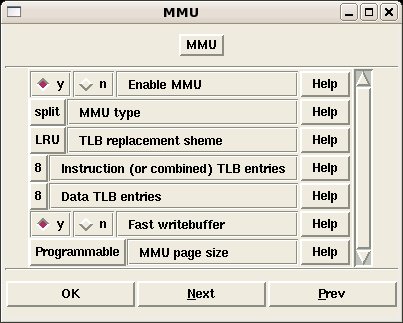

NextボタンをクリックするとMMUの設定GUIウィンドウが立ち上がります。

MMU有り無しを選ぶことができます。Linuxを動かすためにはMMUは必ず必要ですからEnable MMUはYにします。

(MMU無しの場合は、uClinuxというMMU無しのシステムのための特殊なlinuxを使用することができます。)

MMUも細かく設定可能ですが、ここでも設定を変更しません。

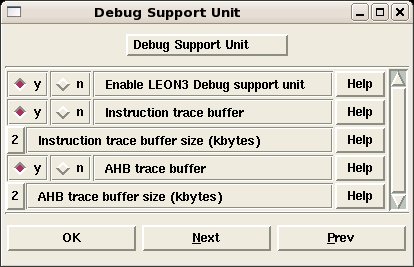

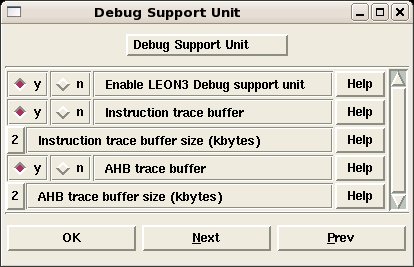

Next ボタンをクリックすると、Debug support unitのコンフィグレーションに関する設定GUIが立ち上がります。

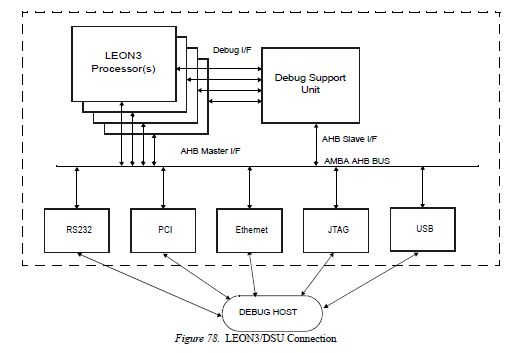

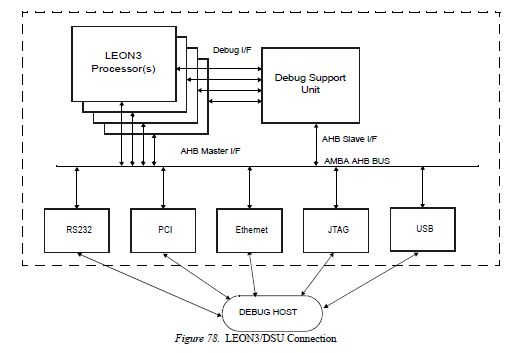

Debug support unitとは、LEON3プロセッサと密接に結合してregisterの値等を読み取り、ホストコンピュータ上で実行されているプログラム Grmon と通信を行うハードウェアIPです。以下にマニュアル中の概念図を示します。

RS232CやEthernet等、様々なインターフェースでホストコンピュータ上のプログラムGrmonと通信できます。

Debug Support UnitはAMBAマスターでもあるので、各種周辺IPのレジスタ値等も読み取ることができ、ホストコンピュータ上に表示することが可能です。

当然Debug support unitは使用します。ここも設定はこのままで Next ボタンをクリックします。

Fault tleranceに関するGUIが立ち上がります。

SEUに対するFault tleranceバージョンのLEONプロセッサはGPLライセンスでは公開されていません。このGUIでは何も設定できません。

Next ボタンをクリックします。

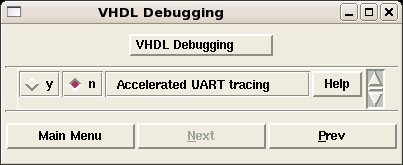

VHDLのデバッグに関するGUIが立ち上がります。ここもこのまま変更しません。

ここまでで、LEON3プロセッサに関するコンフィグレーションが出来ました。次にAMBAバスに接続されるIP群に関してコンフィグレーションを行っていきます。

Next ボタンをクリックします。

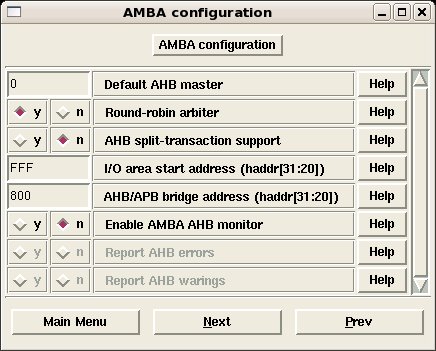

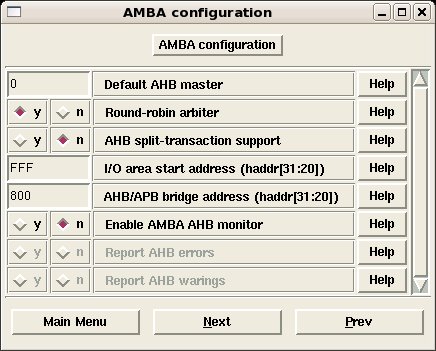

まず、AMBAバスそのものの設定GUIが立ち上がります。

デフォルトAHBマスターは0番、アービターはラウンドロビン、split, retryは使わない等の設定を行っています。

ここもこの設定のまま、Nextボタンを押します。

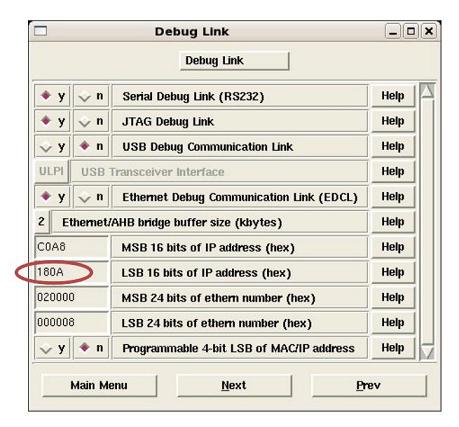

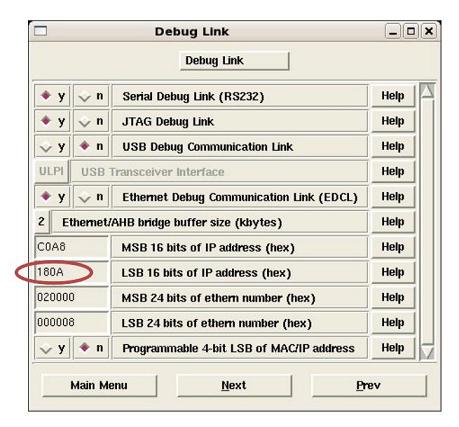

Debug Linkに関する設定GUIが立ち上がります。

Debug Linkとは、このエントリで説明したDebug Support Unitとホストを接続するためのハードウェアのことを指しています。

ま

ず、何か問題があった場合にもっとも接続できる可能性が高いRS232C接続のためのハードウェアは使用になれるまでは付けておきます。JTAG

Debug LinkはFPGAのJTAGを利用して接続するためのものです。USB Debug Communication LinkはDebug

support unitとの通信のみができるUSBターゲットハードウェアです。ここでは使用せずに、次のEthernet Debug

Communication Link(EDCL)を使用します。

EDCLとは、このエントリの図に出てくるようにEthernet MACコアの中に埋め込む Debug Support Unitと接続するための専用ハードウェアのことです。

Ethernet接続ですので、RS232Cより圧倒的に転送速度が速いです。Linuxのイメージは結構大きくなることもありますので、こちらを使用できるようにします。

EDCL

はFPGAにマッピングした直後、ソフトウェアが何も搭載されていない状態で動作しなければいけません(ソフトウェアの転送自体を行うため)。よって

Linuxが立ち上がった後にEthernet通信を行うIPアドレスとは別にEDCL自体がIPアドレスを持っています。GUI上でそのIPアドレスを

設定するのですが、これはハードウェアに組み込まれます。RS232C経由でGRMON通信を行いEDCLのIPアドレスを書き換えることもできるのです

が、二度手間になるので直接通信できるようにします。

私

のネットワーク環境では、192.168.24.*** のIPアドレスしか許されないため、

192.168.24.10 をEDCLに割り当てました。図中の赤い楕円の部分を書き換えています。ここは各自のネットワーク環境に合わせたIPアドレ

スをHEXで入力してください。

その他の部分はそのままで、Nextをクリックします。

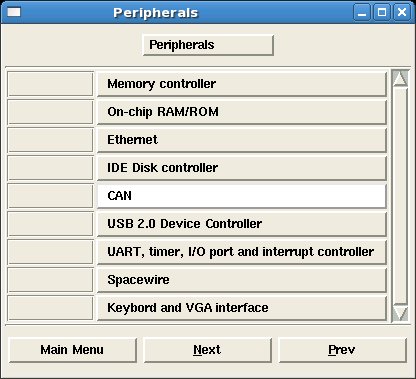

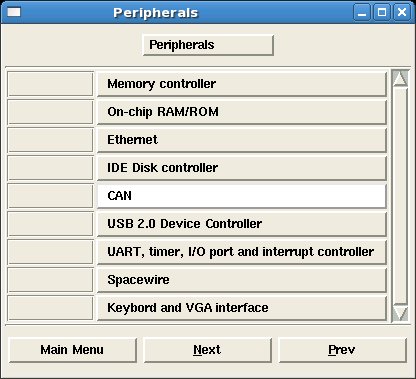

周辺IPに関する設定GUIが立ち上がります。

AMBAバスにつながる周辺IPの設定をこれから行っていきます。どのIPを接続するかもここで決めます。

Nextをクリックします。

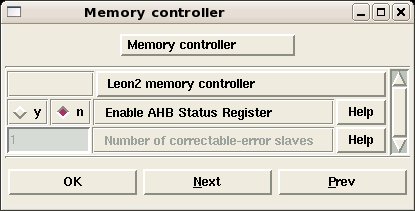

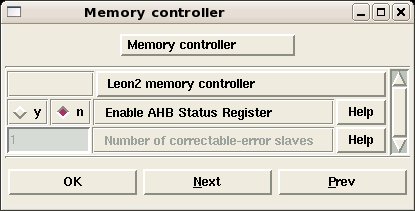

メモリコントローラの設定GUIが立ち上がります。

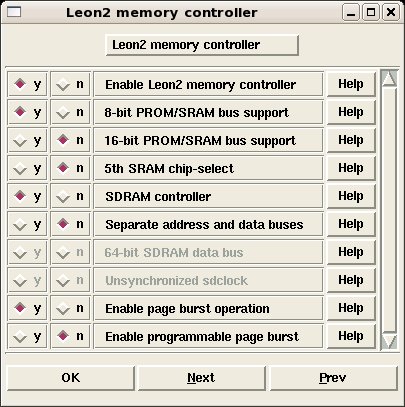

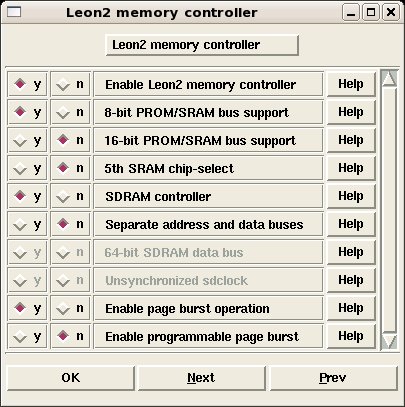

Leon2メモリコントローラGUIが立ち上がりますのでそのまま Next ボタンを押します。

様々なバスタイプを設定できるようになっています。ここもすでにGR-XC3S-1500のメモリに合わせてデフォルト設定されていますので、このまま Next ボタンを押します。

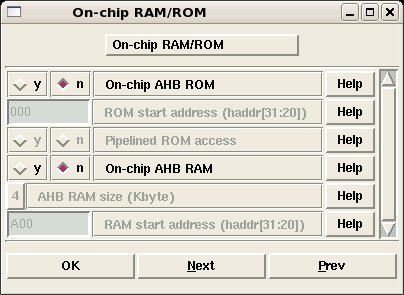

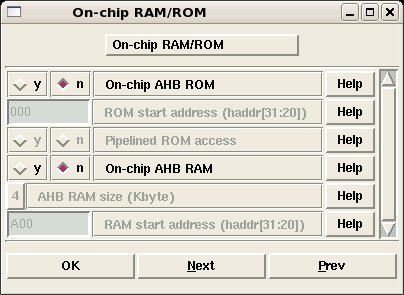

On-chip ROM/RAMに関する設定GUIが立ち上がります。

これらはAMBA AHBバスにつながるRAM,ROMです。今回特に必要としないので、そのまま Next ボタンを押します。

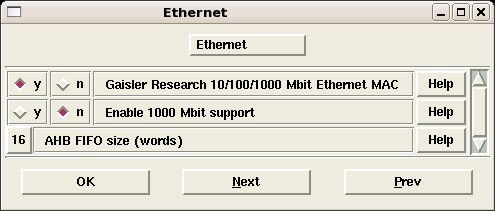

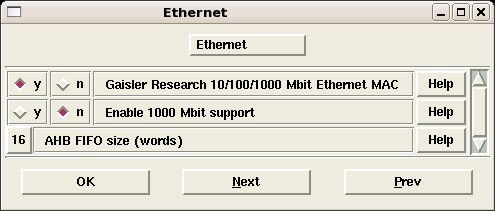

Ethernetコアの設定GUIが立ち上がります。

今回Ethernetコアを使用しますので、最初のチェックボックスは y となっています。

2番目のチェックボックスはギガビットイーサネットを使用するかどうかですが、ギガビットイーサネットコアはコマーシャルライセンスのみとなっています。よって n となっています。

FIFOサイズはデフォルトのままで Next ボタンを押します。

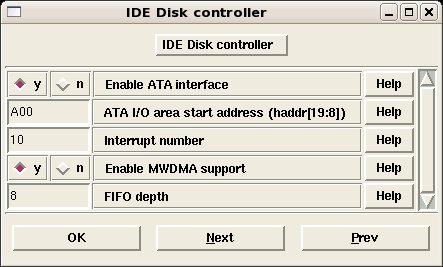

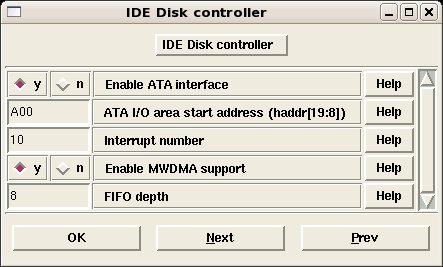

IDE Disk controllerの設定GUIが立ち上がります。

IDE Disk controllerは今回は使用しませんが、FPGAサイズに余裕があるため、デフォルトのままでAMBAバスに接続します。Nextボタンをクリックします。

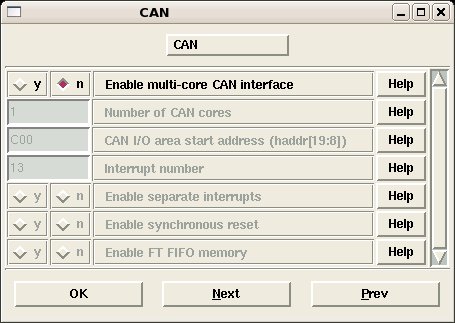

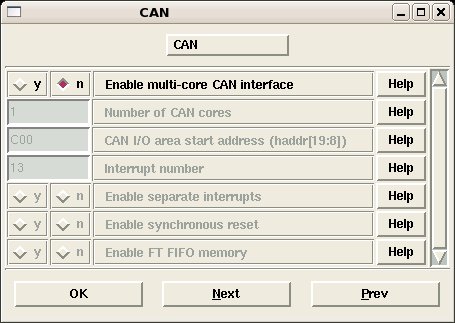

CANの設定GUIが立ち上がります。

今回CANは使用しません。Nextボタンをクリックします。

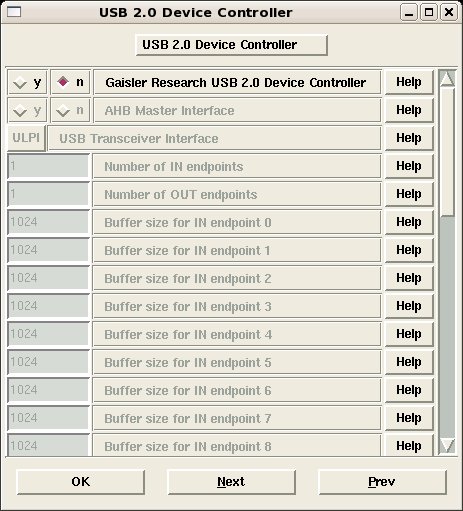

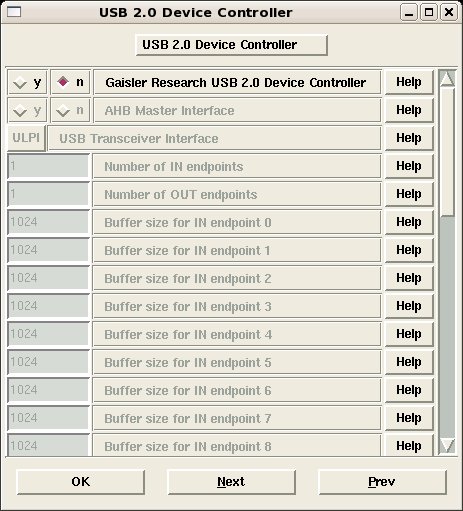

USBに関する設定GUIが立ち上がります。

USBはコマーシャルライセンスのみですので使用できません。

Nextボタンをクリックします。

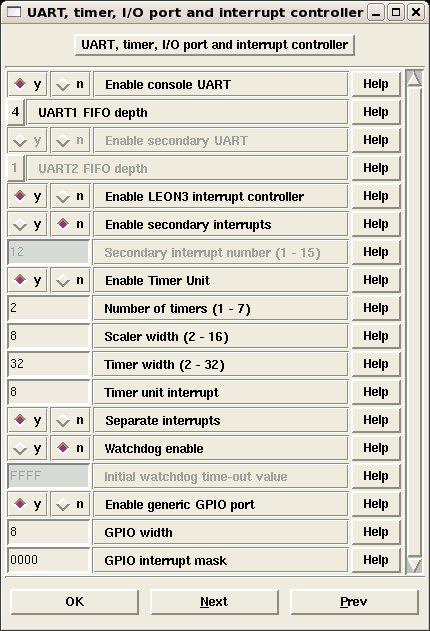

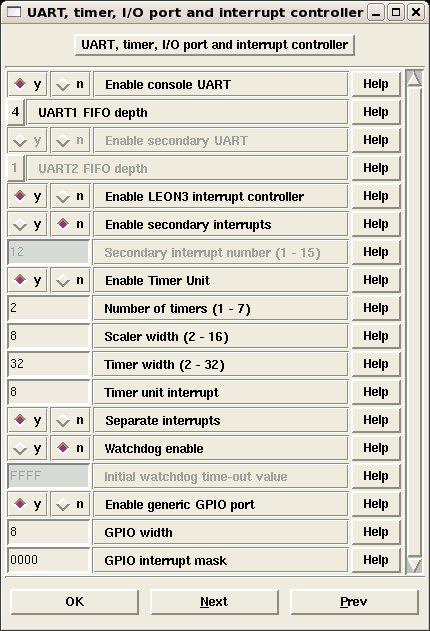

UART,Timer,割り込みコントローラ, GPIOに関する設定GUIが立ち上がります。

Linuxをブートしたときにコンソール出力をUARTにしてteratermでホストに表示する方法とVGAフレームバッファをコンソールにする方法がありますが、ハードウェアとしてのUARTは組み込んでおきます。

割り込みコントローラとタイマーは必須です。

GPIOは無くても動作しますが、FPGAに余裕があるので、デフォルト通りに組み込んでおきます。

ここもデフォルト通り何も変更せずに Next ボタンを押します。

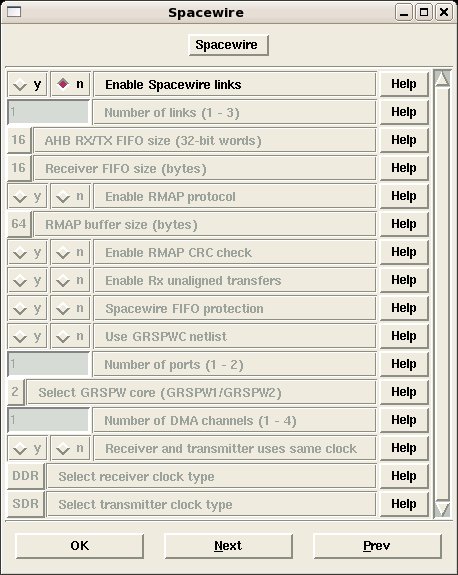

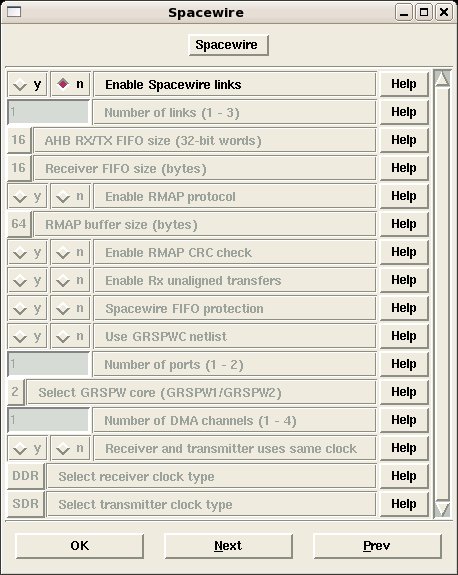

spacewireに関する設定GUIが立ち上がります。

spacewireもGPLライセンスでは公開されていませんので、使用できません。

Next ボタンをクリックします。

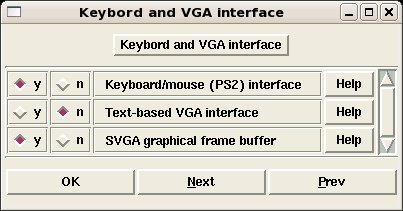

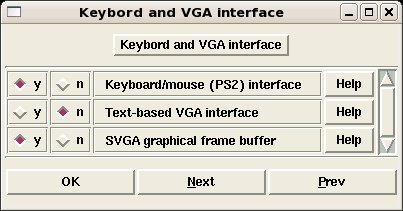

KeyboardとVGA interfaceに関するGUIが立ち上がります。

PS/2インターフェースとVGAフレームバッファを使用します。

Next ボタンをクリックします。

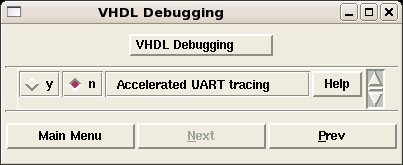

VHDL Debuggingに関するGUIが立ち上がります。

デフォルトのままにします。

設定がすべて終りましたので、Main Menuと書かれているボタンをクリックします。VHDL Debuggingに関するGUIが消えます。

最初に立ち上がったGUIに戻り、 Save and Exitボタンをクリックします。確認されますので、OKボタンをクリックします。

これでコンフィグレーションが終了しました。

公式にサポートされているボードでは、そのボード構成にあわせたコンフィグレーションがデフォルトとして設定されてあるので、ほとんど修正はありません。今回もEDCLのIPアドレスを変更しただけです。

LEONシステムを使い慣れてくると、様々な変更をしたくなってきます。その時は同じ方法でコンフィグレーションを変更します。

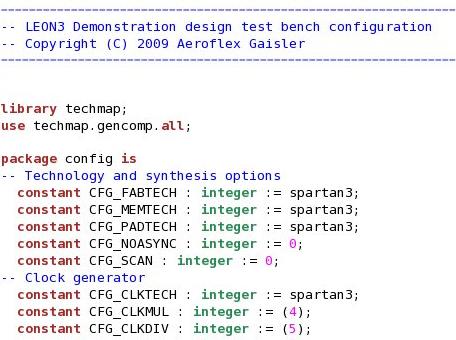

コンフィグレーションを終了すると、同じディレクトリにある config.vhd が変更されます。

実際はこのファイルに変更した変数を記憶させ、各RTLがこのファイルの変数をスイッチとして参照するという仕組みになっています。

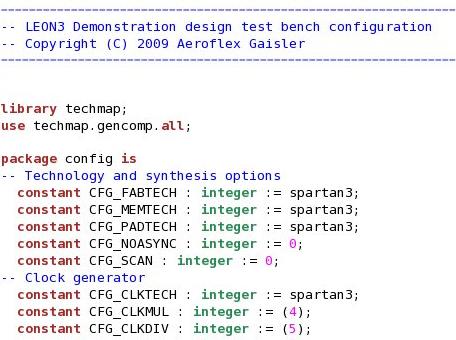

ちなみにconfig.vhdは以下のように定数変数の設定が延々と続くファイルです。

このファイルを各RTLが読み込んでスイッチとしています。

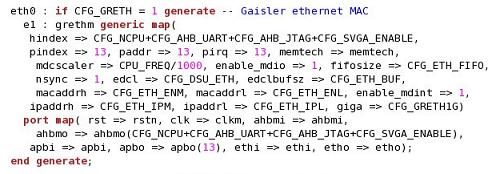

同じディレクトリに leon3mp.vhdというファイルが存在します。これが所謂トップモジュールのRTLです。

これまで設定した周辺IPがLEON3プロセッサにAMBAバスで接続され、FPGAのIOピンと接続されたものです。

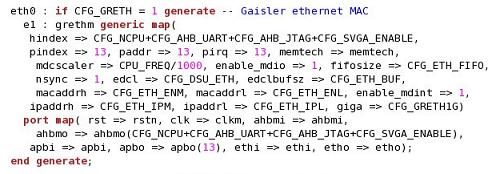

その中の、例えばEthernetコアのインスタンスの部分を読んでみると以下のように記述されています。

config.vhdの中で設定される CFG_GRETHという定数変数の値によってインスタンスするかどうかが決定されていることが分かります。 その他ポートの接続にも多数の定数変数が使用されていることが分かります。

5. LEONシステムのトップ検証

これまでの設定で、トップモジュールRTL leon3mp.vhd が完成しました。

今回はIPをつなぎ変えたりはしていませんが、IPを付けたり外したりした場合にはその接続の検証が必要になります。

それをコンフィグレーション終了後に行います。

ここではGHDLを用いてRTLシミュレーションを行います

(GHDLはgccのテクノロジを利用した、オープンソースのVHDLシミュレーションです)。

同じディレクトリにある、testbench.vhd が、トップモジュールをインスタンスしているトップ検証のためのVHDLソースコードです。SDRAMのRTLや、テスト用のモジュールgrtestmod のRTLも接続されています。

同じディレクトリにsdram.srecというファイルがあります。これは、LEONシステムの基本チェックを行うプログラムをコンパイルして作ったSDRAMの内容としてインクルードされるバイナリです。

こ

のバイナリの内容は、同じディレクトリの systest.c

と、LEON/grlib-gpl-1.0.22-b4095/software/leon3

のディレクトリを見ると理解することができます。とりあえず、LinuxをブートしてLEONシステムを使用してみるためには内容を理解する必要はありま

せん。

まず、以下の実行の前にGHDLにパスが通っていることを確認しておきます。

make ghdl

GHDLのメッセージが大量に出力されて終了します。

同じディレクトリに testbench という実行ファイルが生成されました。

このバイナリを実行することでGHDLシミュレーションが始まります。

./testbench

と実行するとRTLシミュレーションが開始され、以下のようなメッセージが出力されて終了します。

LEON3 GR-XC3S-1500 Demonstration design

GRLIB Version 1.0.22, build 4095

Target technology: spartan3 , memory library: spartan3

ahbctrl: AHB arbiter/multiplexer rev 1

ahbctrl: Common I/O area at 0xfff00000, 1 Mbyte

ahbctrl: AHB masters: 6, AHB slaves: 8

ahbctrl: Configuration area at 0xfffff000, 4 kbyte

ahbctrl: mst0: Gaisler Research Leon3 SPARC V8 Processor

ahbctrl: mst1: Gaisler Research AHB Debug UART

ahbctrl: mst2: Gaisler Research JTAG Debug Link

ahbctrl: mst3: Gaisler Research SVGA frame buffer

ahbctrl: mst4: Gaisler Research GR Ethernet MAC

ahbctrl: mst5: Gaisler Research ATA controller

ahbctrl: slv0: European Space Agency Leon2 Memory Controller

ahbctrl: memory at 0x00000000, size 512 Mbyte, cacheable, prefetch

ahbctrl: memory at 0x20000000, size 512 Mbyte

ahbctrl: memory at 0x40000000, size 1024 Mbyte, cacheable, prefetch

ahbctrl: slv1: Gaisler Research AHB/APB Bridge

ahbctrl: memory at 0x80000000, size 1 Mbyte

ahbctrl: slv2: Gaisler Research Leon3 Debug Support Unit

ahbctrl: memory at 0x90000000, size 256 Mbyte

ahbctrl: slv3: Gaisler Research ATA controller

ahbctrl: I/O port at 0xfffa0000, size 256 byte

apbctrl: APB Bridge at 0x80000000 rev 1

apbctrl: slv0: European Space Agency Leon2 Memory Controller

apbctrl: I/O ports at 0x80000000, size 256 byte

apbctrl: slv1: Gaisler Research Generic UART

apbctrl: I/O ports at 0x80000100, size 256 byte

apbctrl: slv2: Gaisler Research Multi-processor Interrupt Ctrl.

apbctrl: I/O ports at 0x80000200, size 256 byte

apbctrl: slv3: Gaisler Research Modular Timer Unit

apbctrl: I/O ports at 0x80000300, size 256 byte

apbctrl: slv4: Gaisler Research PS2 interface

apbctrl: I/O ports at 0x80000400, size 256 byte

apbctrl: slv5: Gaisler Research PS2 interface

apbctrl: I/O ports at 0x80000500, size 256 byte

apbctrl: slv6: Gaisler Research SVGA frame buffer

apbctrl: I/O ports at 0x80000600, size 256 byte

apbctrl: slv7: Gaisler Research AHB Debug UART

apbctrl: I/O ports at 0x80000700, size 256 byte

apbctrl: slv8: Gaisler Research General Purpose I/O port

apbctrl: I/O ports at 0x80000800, size 256 byte

apbctrl: slv13: Gaisler Research GR Ethernet MAC

apbctrl: I/O ports at 0x80000d00, size 256 byte

clkgen_spartan3e: spartan3/e sdram/pci clock generator, version 1

clkgen_spartan3e: Frequency 50000 KHz, DCM divisor 4/5

leon3_0: LEON3 SPARC V8 processor rev 0

leon3_0: icache 2*4 kbyte, dcache 1*4 kbyte

dsu3_2: LEON3 Debug support unit + AHB Trace Buffer, 2 kbytes

ahbuart7: AHB Debug UART rev 0

ahbjtag AHB Debug JTAG rev 0

apbuart1: Generic UART rev 1, fifo 4, irq 2

irqmp: Multi-processor Interrupt Controller rev 3, #cpu 1, eirq 0

gptimer3: GR Timer Unit rev 0, 8-bit scaler, 2 32-bit timers, irq 8

apbps2_4: APB PS2 interface rev 2, irq 4

apbps2_5: APB PS2 interface rev 2, irq 5

svgactrl6: SVGA controller rev 0, FIFO length: 384, FIFO part length: 128, FIFO address bits: 9

grgpio8: 18-bit GPIO Unit rev 0

greth4: 10/100 Mbit Ethernet MAC rev 04, EDCL 1, buffer 2 kbyte 128 txfifo, irq 13

atactrl3: ATA controller rev 0, irq 10

**** GRLIB system test starting ****

Leon3 SPARC V8 Processor

CPU#0 register file

CPU#0 multiplier

CPU#0 radix-2 divider

CPU#0 cache system

CPU#0 memory management unit

Multi-processor Interrupt Ctrl.

Modular Timer Unit

timer 1

timer 2

chain mode

Generic UART

GR Ethernet MAC

Test passed, halting with IU error mode

testbench.vhd:375:6:@2357898ns:(assertion failure): *** IU in error mode, simulation halted ***

./testbench:error: assertion failed

./testbench:error: simulation failed

最後にエラーという出力が出ていますが、これで正常終了です。

最初にコンフィグレーションしたLEONシステムの構成が出力され、その後SDRAMに乗っているソフトウェアに従い、様々なモジュールのチェックされて行きます。

独立したプロセッサシステムをソフトウェアバイナリによって検証するという方法を取っているため、シミュレーションを終了させる方法がIUを無理やりエラーモードに入れるしかありません。

よって、 testbench.vhd:375:6:@2357898ns:(assertion failure): *** IU in error mode, simulation halted ***と表示された場合は無事シミュレーションが終了したということです。

これでトップ検証が終了しました。

6. LEONシステムのFPGAマッピングとGRMON通信

これまでで生成したLEONシステムをFPGAにマッピングします。

これまでの作業と同じく、LEON/grlib-gpl-1.0.22-b4095/designs/leon3-gr-xc3s-1500 のディレクトリで作業を行います。まず、ISEへのパスが通っているか確認します。パスが通っていない場合は、

source /opt/Xilinx/11.1/settings32.sh

によってパスを通しておきます。

make ise-launch

と打ち込むと、ISEのプロジェクトファイルが作成され、自動的にISEのウィンドウが立ち上がります。

後

は通常のISEのマッピングと同じく、generate programing fileをRUNさせるだけで、FPGAへ論理合成、配置配線を行って

bit ファイルを作成してくれます。オプションを変更したい場合はRUNさせる前に行います。今回はオプションを変更する必要はありません。

ISEをバッチモードで動作させてウィンドウを立ち上げずにbitファイルまで作ってしまうコマンドも用意されています。慣れてきたらこちらに変更することも可能です。

たったこれだけでFPGAマッピングが終了しました。

IPの追加等を行ったときは、同じディレクトリにある ucf ファイルのピン配置を変更する必要があります。

公式サポートボード以外の場合は、似たボードの設定をコピーしてきて、ucfファイルを変更したりターゲットデバイスを変更したりする必要があります。

ここまで行ってbitファイルができたら、実際にマッピングします。

ボードに電源ケーブル、FPGAコンフィグケーブル、イーサネットケーブル、RS232Cケーブルを接続します。

(ディスプレイはこのタイミングでは必要ありません。)

私の場合は、digilent社のUSB-JTAGケーブルを用いていますので、SAMBA経由でウィンドウズにbitファイルを送り、digilent社のソフトAdeptを立ち上げてFPGAのコンフィグレーションを行いました。

Xilinxの純正ケーブルの場合はISEに付属しているIMPACTというソフトでFPGAのコンフィグレーションを行います。

また、RS232Cケーブルは私のPCにはRS232C端子が無いのでUSB-RS232C変換ケーブル(ATEN製)を使用しました。

ボード上の Done のLEDが点滅したらFPGAコンフィグレーション完了です。

ハードウェアが完成したので、ソフトウェアのコンパイルに進んでも良いのですが、ここでハードウェアがきちんと動作するか確認しておきます。

GR-XC3S1500は、gaisler research社からlinuxのコンパイル済みサンプルイメージをダウンロードすることができます。

LinuxのダウンロードページのSample Linux 2.6 images for LEON3の項から、GR-XC3S-1500用のコンパイル済みイメージ image.dsu をダウンロードしてきます。

このサンプルイメージはUARTにコンソール出力を行います。RS232Cをつないだホストコンピュータのwindows上にコンソール出力を表示するためのソフトteratermをインストールして準備しておきます。

teratermを立ち上げ、接続先をシリアル(私の環境では、COM3)に設定します。

teratermの"設定"プルダウンからシリアルポート設定を選択します。

ボー・レート 38400

データ 8bit

パリティ none

ストップ 1bit

フロー制御 none

に設定します。これでコンソール出力を表示する準備が整いました。

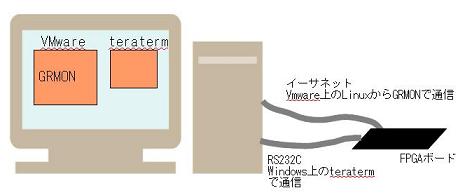

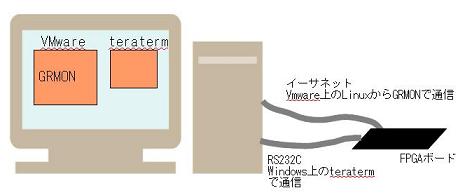

以下のような接続イメージです。

次にGRMONを立ち上げて、コンフィグレーションの時に出てきたDebug Support Unitと通信を行います。

grmon/grmon-eval/linux/grmon-eval -nb -nswb -eth -ip 192.168.24.10

と打ち込みgrmonを起動します。-ethに続けて打ち込むIPアドレスはコンフィグレーションの時に出てきたEDCLのIPアドレスです。無事にFPGAボードのEDCLと通信ができると以下のようなメッセージが出力されて入力受付状態になります。

GRMON LEON debug monitor v1.1.41 evaluation version

Copyright (C) 2004-2008 Aeroflex Gaisler - all rights reserved.

For latest updates, go to http://www.gaisler.com/

Comments or bug-reports to support@gaisler.com

This evaluation version will expire on 28/1/2011

ethernet startup.

GRLIB build version: 4095

initialising ...............

detected frequency: 40 MHz

Component Vendor

LEON3 SPARC V8 Processor Gaisler Research

AHB Debug UART Gaisler Research

AHB Debug JTAG TAP Gaisler Research

SVGA Controller Gaisler Research

GR Ethernet MAC Gaisler Research

ATA Controller Gaisler Research

LEON2 Memory Controller European Space Agency

AHB/APB Bridge Gaisler Research

LEON3 Debug Support Unit Gaisler Research

Generic APB UART Gaisler Research

Multi-processor Interrupt Ctrl Gaisler Research

Modular Timer Unit Gaisler Research

PS/2 interface Gaisler Research

PS/2 interface Gaisler Research

General purpose I/O port Gaisler Research

Use command 'info sys' to print a detailed report of attached cores

grlib>

ここでinfo sysと入力すると、現在のFPGAにマッピングされているLEONシステムの構成がレポートされます。

grlib> info sys

00.01:003 Gaisler Research LEON3 SPARC V8 Processor (ver 0x0)

ahb master 0

01.01:007 Gaisler Research AHB Debug UART (ver 0x0)

ahb master 1

apb: 80000700 - 80000800

baud rate 115200, ahb frequency 40.00

02.01:01c Gaisler Research AHB Debug JTAG TAP (ver 0x0)

ahb master 2

03.01:063 Gaisler Research SVGA Controller (ver 0x0)

ahb master 3

apb: 80000600 - 80000700

clk0: 25.00 MHz clk1: 40.00 MHz clk2: 50.00 MHz clk3: 65.00 MHz

04.01:01d Gaisler Research GR Ethernet MAC (ver 0x0)

ahb master 4, irq 13

apb: 80000d00 - 80000e00

edcl ip 192.168.24.10, buffer 2 kbyte

05.01:024 Gaisler Research ATA Controller (ver 0x0)

ahb master 5, irq 10

ahb: fffa0000 - fffa0100

Device 0: (None)

Device 1: (None)

00.04:00f European Space Agency LEON2 Memory Controller (ver 0x1)

ahb: 00000000 - 20000000

ahb: 20000000 - 40000000

ahb: 40000000 - 80000000

apb: 80000000 - 80000100

8-bit prom @ 0x00000000

32-bit sdram: 1 * 64 Mbyte @ 0x40000000, col 9, cas 2, ref 7.8 us

01.01:006 Gaisler Research AHB/APB Bridge (ver 0x0)

ahb: 80000000 - 80100000

02.01:004 Gaisler Research LEON3 Debug Support Unit (ver 0x1)

ahb: 90000000 - a0000000

AHB trace 128 lines, 32-bit bus, stack pointer 0x43fffff0

CPU#0 win 8, hwbp 4, itrace 128, V8 mul/div, srmmu, lddel 1

icache 2 * 4 kbyte, 32 byte/line lru

dcache 1 * 4 kbyte, 16 byte/line

01.01:00c Gaisler Research Generic APB UART (ver 0x1)

irq 2

apb: 80000100 - 80000200

baud rate 38461

02.01:00d Gaisler Research Multi-processor Interrupt Ctrl (ver 0x3)

apb: 80000200 - 80000300

03.01:011 Gaisler Research Modular Timer Unit (ver 0x0)

irq 8

apb: 80000300 - 80000400

8-bit scaler, 2 * 32-bit timers, divisor 40

04.01:060 Gaisler Research PS/2 interface (ver 0x2)

irq 4

apb: 80000400 - 80000500

05.01:060 Gaisler Research PS/2 interface (ver 0x2)

irq 5

apb: 80000500 - 80000600

08.01:01a Gaisler Research General purpose I/O port (ver 0x0)

apb: 80000800 - 80000900

grlib>

接続された各種IPのAMBAアドレスが表示されました。

それでは、先ほどダウンロードしてきたlinuxイメージimage.dsuをFPGAにロードして実行します。

load image.dsu

run

と入力するとlinuxのブートがはじまり、teratermに続々とlinux boot messageが流れていきます。

無事にブートできteraterm上てlinuxのコマンド受付状態になればブート成功です。

これで、FPGAにマッピングしたハードウェアが正しく動作していることが確認できました。

今回はコンパイル済みのlinux imageを動作させただけですので、次から自分でlinuxをコンパイルしてブートイメージを作る方法に入ります。

6. LEONシステム Linuxコンパイル

ハードウェアのマッピングは終了しました。ここからLinuxのバイナリーイメージの生成に入ります。

基本的にgaisler researchのHPからダウンロードした snapgear linuxをコンフィグレーションしてmakeするだけでバイナリーイメージを生成することができます。

まず、gaisler researchのHPから、linuxクロスコンパイル用の GNU toolchainをインストールしていることを確認します。そして、そこにパスが通っていることを確認します。

snapgear linuxのソース自体もgaisler researchのHPからダウンロードします。

その際に snapgear-manual-p**.pdf というsnapgear linuxをLEONシステムで使用するためのマニュアルもダウンロードします。このマニュアルは、かなり詳細に記述されていますので問題があった時に参考にします。

ダウンロードしたソースコードを解凍したときにできたディレクトリ snapgear-2.6-p42に移動してコンフィグレーションを開始します。

cd snapgear-2.6-p42

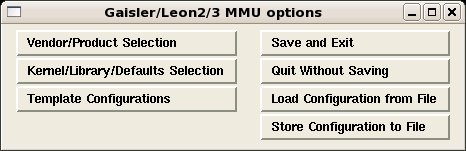

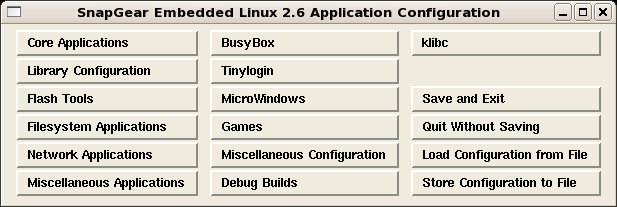

make xconfig

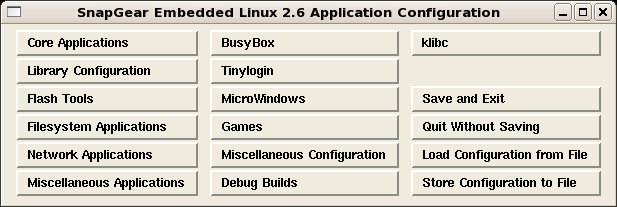

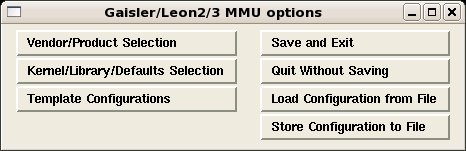

と打ち込むと、コンフィグレーションGUIウィンドウが立ち上がります。

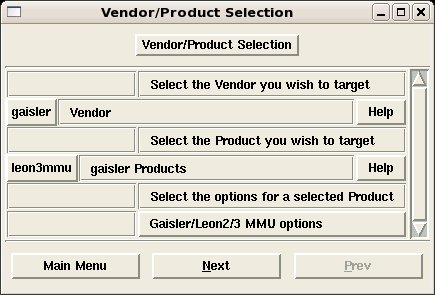

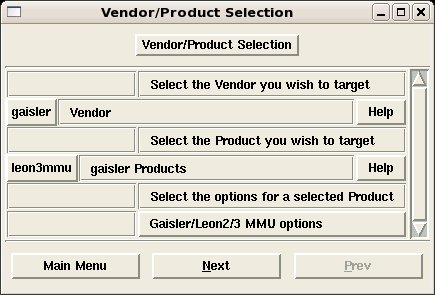

まず、Vendor/Product Selectionのボタンをクリックします。

Vendorはgaisler, TargetはLeon3mmuです。このまま、Nextボタンをクリックします。

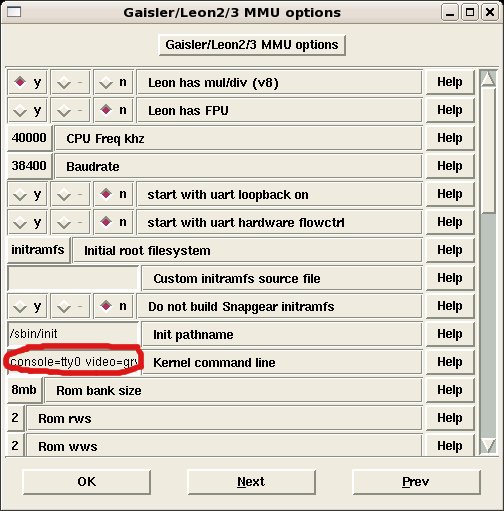

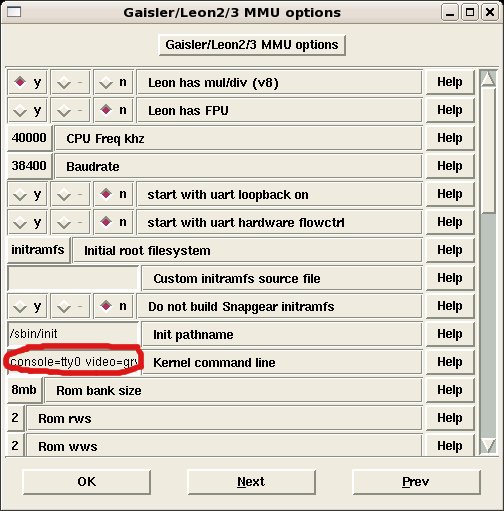

Mul/DivのハードウェアはLEON3ハードウェアのコンフィグレーションで実装したので、yに変更します。

FPUは無しにしたので、nのままです。

この二つのオプションはクロスコンパイラのコンパイル時のオプションとして与えられます。

CPUの周波数とボー・レートを入力します。

UARTは今回使用しないのでnにします。

ルートファイルシステムは initramfsです。

kernel command lineは、デフォルトでは、UARTをコンソール出力指定しています。ハードウェアコンフィグレーションの時にSVGAフレームバッファIPを接続したので、フレームバッファがコンソールになるように変更します。

今回は以下のように記述しました。

console=tty0 video=grvga:640x480@60,16,614400

これでVGAサイズのフレームバッファがコンソールとなります。

ここの設定値については、ダウンロードしたsnapgear-manual-p**.pdfや、snapgear-2.6-p42/linux-2.6.21.1/Documentation/kernel-parameters.txtに詳細が書かれています。

ROMサイズについてはそのままで、Nextボタンをクリックします。

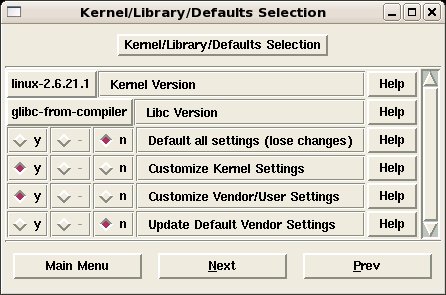

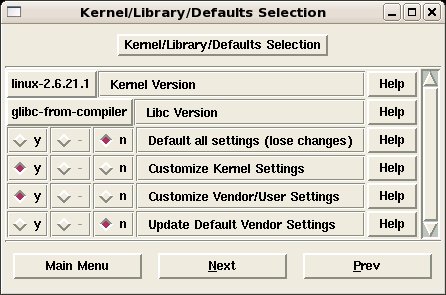

Kernel Versionは、2.6.21.1を選びます。

Customize Kernel Settings と Customize Vendor/User SettingsをyにしてNextをクリックします。

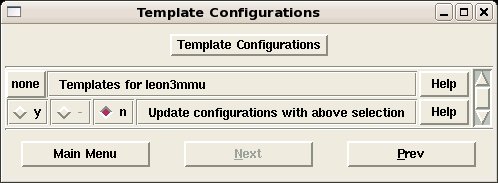

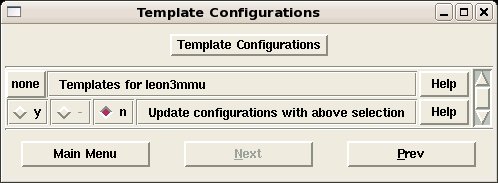

template configurationはそのままで Main menu buttonをクリックします。

最初に立ち上がったGUIに戻り、Save and Exitボタンをクリックします。

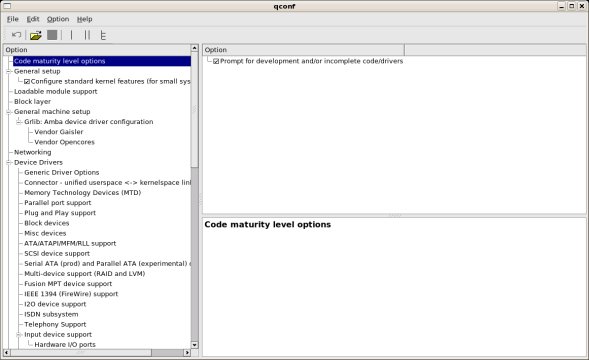

Customize kernel settingsをyにしたので、Linux kernelのコンフィグレーションGUIが立ち上がります。

上の方の General machine setup の中に Grlib:Amba device driver configurationという項目が見えます。

そこをクリックすると、 /proc filesystem for ambaにチェックが入っていることが分かります。

そこはそのままで、その下の Print AMBA PnP infoにチェックが入ってないので入れます。

ここにチェックを入れておくと、立ち上げの時にAMBAバス構成の情報がコンソールに現れます。

さ

らに下のVendor Gaislerをクリックすると Grlib gpio

driverにチェックが入っていませんが、GPIOはとりあえず使わないのでこのままにします。 Grlib apbuart driver と

Grlib apbuart serial

consoleにはチェックが入っています。コンソールはフレームバッファにするのですが、動作しなかった場合はUARTが重要な通信手段となる可能性が

あるのでチェックを入れたままにします。

Grlib

の項目の下の方に Networkingという項目があります。Ethernet通信を行いますので Networking

supportにはチェックを入れます。Unix domain sockets とTCP/IP

networkingを有効にします。そこで出てくるkernel level autoconfigurationにもチェックを入れます。

次にDevice Driversの項目に入ります。

Memory Technology Devicesにチェックを入れます (すみません、ここら辺は詳細を良く分かってません。。。)。

Block Devices

Network

device support にチェックを入れます。さらにその下の Ethernet(10 or

100Mbit)にチェックを入れます。その時出てくる Generic Media Independent interface device

supportにもチェックを入れます。

Input Device support にチェックを入れます。さらにその下のKeyboardsにもチェックを入れます。

Input Device support の下にある、Hardware IO portsをクリックします。そこで出てくる grlib ps2 keyboard controllerにチェックを入れます。

さ

らに下の方に行って、Graphics supportをクリックします。そこで出てくる Support for frame buffer

devicesにチェックを入れます。Gaisler svga framebuffer supportにもチェックを入れます。

Graphics

supportの下にある、Console display driver supportをクリックします。そこで出てくる Frame

buffer console supportにチェックを入れます。そこで出てくるSelect

compiled-in-fontsをクリックします。さらにそこに出てくるVGA8x16 fontをクリックします。

Graphics supportの下に出てくる Logo configurationをクリックします。そこで出てくる Bootup logoにチェックを入れます。

さらに下の方にいって、File systemsをクリックします。そこで出てくる Second extended fs supportにチェックをいれます。

(kenrlコンフィグについては、私はあまり詳しくありません。間違いがあれば教えてください)

FileメニュからSaveした後にexitします。

最初にCustomize/vender user settingをyにしたので、次にユーザランドのアプリケーション設定GUIが自動的に立ち上がります。

今回はとりあえずブートさせるだけなので、何も変更しません(例えばアプリケーションをデバッグする時などはgdbserverにチェックを入れます)。

コンフィグレーションGUIを立ち上げたターミナルに戻り make と打ち込むことによってlinuxのコンパイルが始まります。

これで、イメージはできたのですが、スタートアップの時にネットワークが接続されていた方が都合が良いので、少しファイルをいじります。

snapgear-2.6-p42/romfs/.... がイメージのルートファイルシステムとなります。

snapgear-2.6-p42/romfs/etc/init.d/rcS がブート時に読み込まれて実行されます。

中身を見てみると、ネットワークを立ち上げている部分がありますが、IPアドレスが私の環境では許されない値になっています。その一行を変更します。

/sbin/ifconfig eth0 up 192.168.24.80

これでブート終了時にネットワークにつながっているはずです。

ファイルを変更したので、イメージを作りなおします(カーネルのコンパイルは必要ありません)。

snapgear-2.6-p42 のディレクトリで以下のようにmakeします。

make image

これでイメージが作りなおされます。

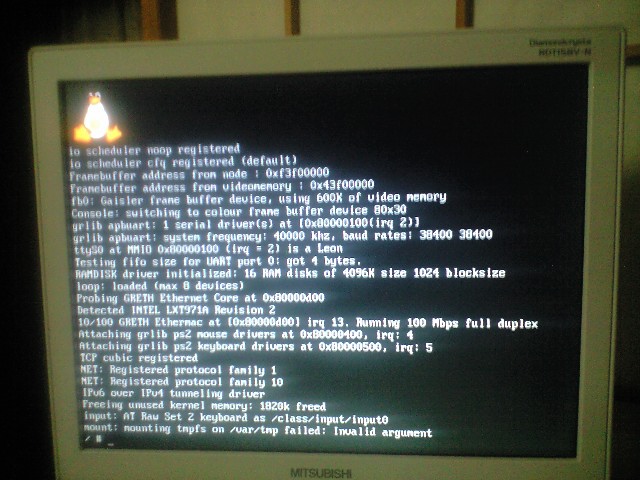

それでは、以前コンパイル済みのイメージをブートしたのと同じ方法で、今回コンパイルしたイメージをブートしてみます。

今回は、コンソールがフレームバッファになり、キーボード入力はPS/2入力となりましたので、ディスプレイとキーボードを接続します。

FPGAにハードウェアをマッピング済みであることを確認します(done LEDが点灯している)。

grmon/grmon-eval/linux/grmon-eval -nb -nswb -eth -ip 192.168.24.10

と入力してDebug support Unitと通信を確立します。

無事接続されたら、以下のようにコンパイルしたイメージを転送し、実行します。

load snapgear-2.6-p42/images/image.dsu

run

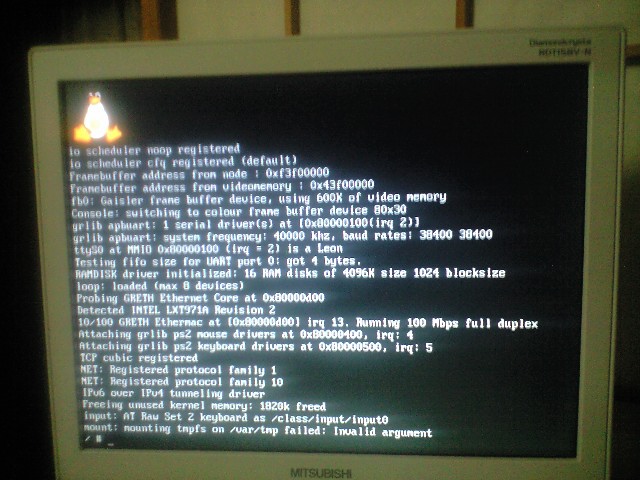

しばらく経つと、、、、、

ディスプレイに見慣れたペンギンマークが現れて、ブートメッセージが流れていきます。

最後にコマンド受付状態になります。

ホストコンピュータに向けた ping コマンドをキーボードから入力して実行すると無事にネットワークが接続されていることが分かります。

Linux ブート成功!!!